L4无人驾驶计算平台是限制L4无人驾驶大规模推广的瓶颈之一,其他瓶颈也很多。悲观的话,10年内L4级无人驾驶无法量产,乐观的话至少也要再等上5年。

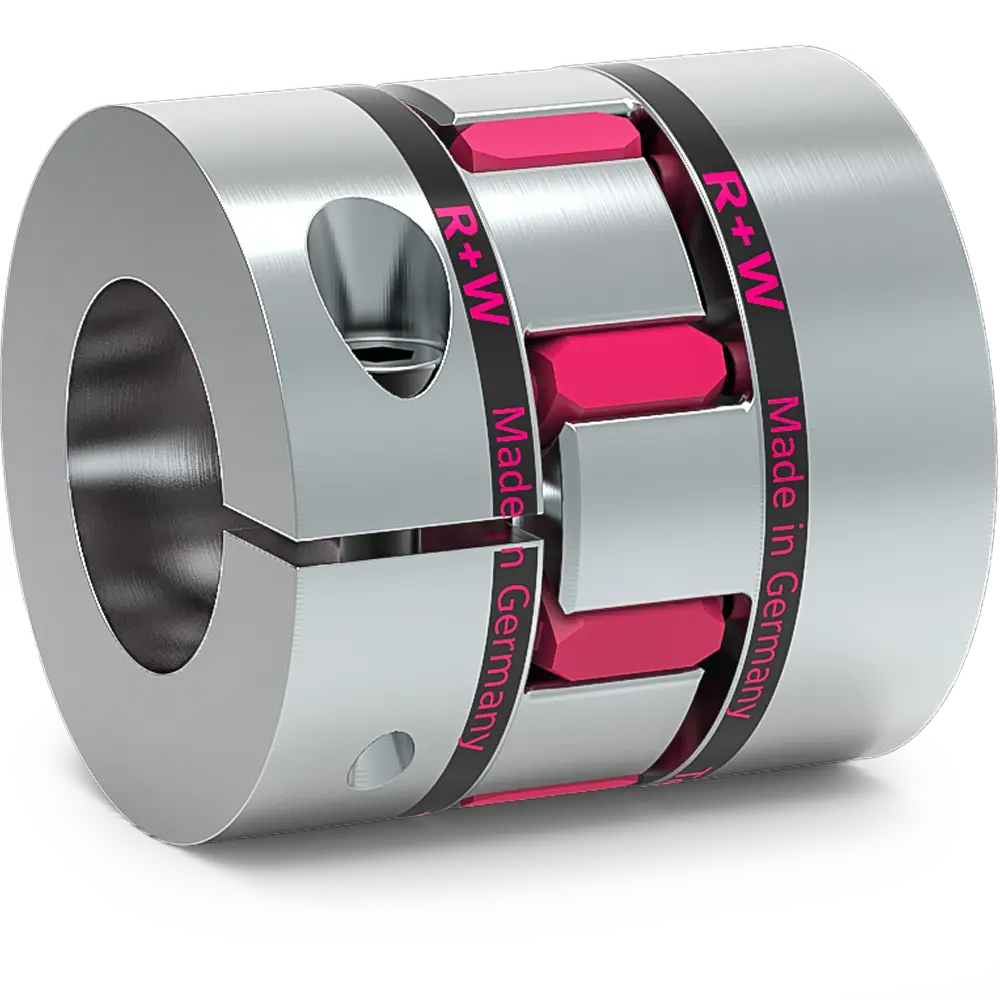

典型L4级无人驾驶计算平台如上图,基本上就是两套一模一样的系统,包含了CPU、GPU和加速器。多个加速器还需要一个PCIe交换机,其价格非常昂贵,甚至比加速器都贵。与线控底盘连接需要一个达到ASIL-D级的MCU,通常是英飞凌的TC297/397,瑞萨的RH850和NXP的MPC574X系列也能达到。

计算平台核心是以太网交换机,以上图为例,Marvell的7口以太网交换器88E6321通过以太网物理层Marvell的88E1512与两个CPU也就是英伟达的Tegra Parker连接。Parker外接GPU加速器,以太网交换器也连接主要传感器和底盘控制MCU(PX2中就是英飞凌的TC297T),可谓是PX2的关键芯片。88E6321的后续产品是88Q5050,由德国大陆汽车旗下子公司Elektrobit与Marvell联合打造,88Q5050则用在英伟达最新旗舰Pegasus,这也是基于最新的车载以太网标准TSN的首次实际应用。

通常CPU对应标量计算,主要是路径规划和决策算法,此外部分激光雷达使用ICP点云配准算法,CPU比GPU能更好对应。常用的传感器融合如卡尔曼滤波算法也多是标量运算。GPU对应矢量或者说向量计算,包括高精度地图、传统视觉算法。矩阵就是卷积运算的核心,也是所谓人工智能的核心运算。通俗一点理解的话,我们可以将标量视为零阶张量,矢量视为一阶张量,那么矩阵就是二阶张量。FPGA比较特殊,它天生并行结构,对应矢量和矩阵都没问题,对应高阶张量更能发挥特长。

CPU应该达到200K DMIPS以上的算力。ARM设计的针对L4使用的Cortex-a76AE,ARM推荐的是惊人的16核设计,车规级肯定运行频率不能太高,否则功耗太高,估计最高不超过2.2GHz,甚至是1.8GHz,这样的算力超过250K,我们给它打个八折,算200K。AI部分主要是推理,一般都是INT8的精度。如果特别侧重摄像头,INT8至少要有20TOPS的算力,如果更侧重激光雷达,那么个人认为4TOPS就足够。

常见或有潜力成为无人驾驶计算平台的芯片对比

EyeQ5的CPU很弱,只有52K,是所有芯片里最差的,不过这关系不大,因为它属于英特尔,英特尔的汽车SoC也就是Atom 3900系列可以派上用场,3900系列中最高级的A3960大约有50K DMIPS。英特尔的Atom 3900系列差不多6年都没更新换代了。或许2020年会更新。

Xavier表现最全面,CPU算力有137K,仍然不及格。SA8155P是高通骁龙855的车规版,跟麒麟990一样都是7纳米,4个A76加4个A55内核。估计A76的运行频率也会降低,即便是A76火力全开,也难以超过130K。特斯拉的AI很强,不过12个A72最多也就是150K。以特斯拉的出货量,这颗芯片估计最低都要300美元。

最优秀的实际是Xilinx的VersalAI Core,AI算力拥有压倒性优势,最低都有49TOPS。这是全球首颗7纳米FPGA。

称之为FPGA或许不切合实际,Xilinx称之为Adaptive Compute Acceleration Platform (ACAP)。

ACAP结合了CPU和GPU(DSP)的高效率应用场景,能够自适应各种计算形式。

ACAP里包含了两个A72内核,对应标量计算,两个A72拥有48KB/32KB的一级缓存,1MB的二级缓存,这比传统的ASIC要高不少。同时也有Cortex-R5双核保证实时性任务的可靠执行,如Boot。有AI和DSP引擎,AI引擎从128-400个,DSP引擎从928-1968个。还有完整的片上网络,包括两个以太网接口,一个USB 2.0,两个UART,两个SPI,两个I2C,两个特别为汽车行业考虑的CAN-FD。LUT方面最高接近200万个,Xilinx说足以媲美服务器级CPU。

Xilinx Versal AICore参数见上表,这么牛掰的东西使用的晶体管数量惊人,Versal AI Core的旗舰VC1902使用了370亿个晶体管,预计最低级的VC1352也有50亿个。而英伟达的Tesla V100才212亿个,Xavier才90亿个晶体管。上个月英特尔还有更疯狂的Stratix 10 GX 10M FPGA。这是全球密度最高的 FPGA,拥有 1020 万个逻辑单元,433 亿颗晶体管。通常芯片的晶体管密度是25-31百万/平方毫米,Xilinx Versal AI Core最小都有大约250平方毫米的裸晶面积,这就注定其价格非常高昂。现在7纳米的产能非常紧俏,FPGA的裸晶面积又特别大,但量又很低,笔者估计最低价格也是1500美金起。ACAP主要市场还是数据中心领域、5G基站和航天航空雷达领域。不过在汽车领域可以只用一片,甚至可以连风扇都不需要的小盒子搞掂L4运算平台。

Versal ACAP在今年9月份正式推出,目前价格还未知。ACAP的出现或许表明初创公司做AI芯片不是个好方向,先不要说7纳米一次流片费用近3亿(28纳米的芯片晶体管密度根本无法和7纳米比)。即便是ASIC,一味强调算力,也根本无法和FPGA匹敌的。灵活度就更不用说了。初创公司还是做算法比较合适,等壮大了,才能烧钱做芯片。

广告

广告

广告

广告