是德科技推出System Designer和Chiplet PHY Designer,优化基于数字标准的仿真工作流程

· 借助由仿真驱动的虚拟合规性测试解决方案,采用更智能、更精简的工作流程,提高 PCIe 设计的工作效率

· 具有设计探索和报告生成能力,可加快小芯片的信号完整性分析以及UCIe 合规性验证,从而帮助设计师提高工作效率,缩短新产品上市时间

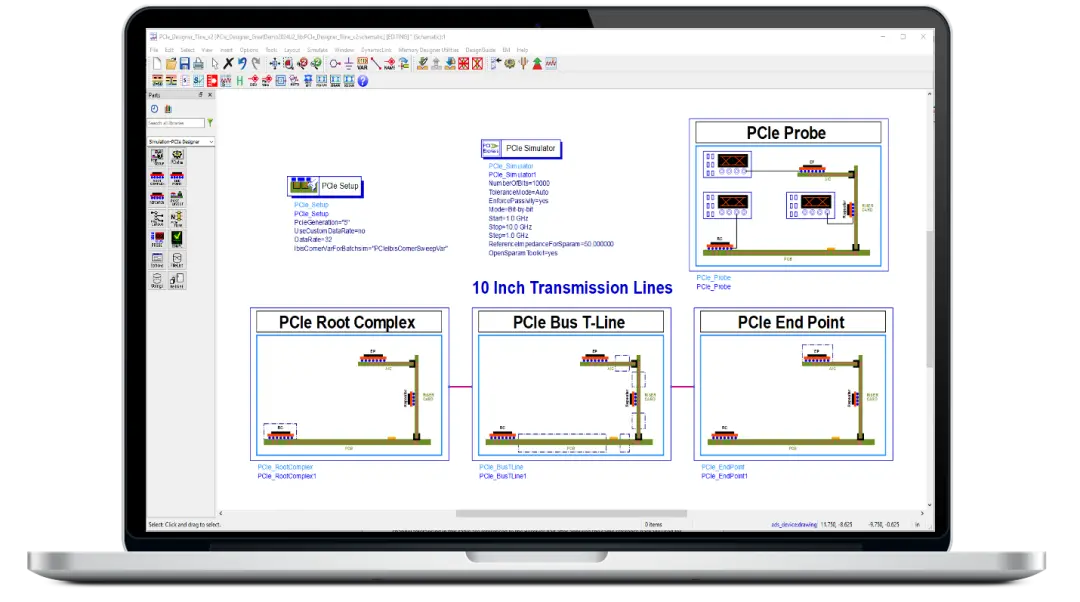

是德科技(Keysight Technologies,Inc.)宣布推出System Designer for PCIe®,这是其先进设计系统 (ADS) 软件套件中的一款新产品,支持基于行业标准的仿真工作流程,可用于仿真高速、高频的数字设计。System Designer for PCIe 是一种智能的设计环境,用于对最新的PCIe Gen5 和 Gen6 系统进行建模和仿真。是德科技还在改进其电子设计自动化平台,通过为现有的 Chiplet PHY Designer 工具增加新功能,评估Chiplet中芯片到芯片的链路裕度性能,并对电压传递函数 (VTF) 是否符合相关参数标准进行测量。

System Designer for PCIe 是一种智能的设计环境

用于对最新PCIe Gen5 和 Gen6 系统进行建模和仿真

PCIe 凭借其高速数字传输能力、出色的可扩展性和适应能力,成为广泛适用于电子行业各领域的重要通用接口标准。它的用途十分广泛,范围涵盖从日常生活中的消费电子设备到高性能计算和关键基础设施系统中的专业应用。

复杂的 PCIe 设计支持多链路和多通道系统,主要涉及 RootComplex 和 End-Point 之间的复杂分析设置,有时还会包括中继器。通常,设计人员需要投入大量时间准备仿真工作,却很容易出错。在仿真过程中,往往缺乏针对特定供应商的算法建模接口(AMI)仿真模型,而实际上在设计周期的早期阶段就需要使用这些模型来探索设计空间。设计师还需要确保他们的原型设计能够在硬件制造开启之前通过合规性测试。

能够提升工作效率、优化工作流程和提高合规性

· System Designer for PCIe能够利用一种智能的设计环境,自动设置多链路、多通道和多层级(PAM4)的 PCIe 系统。它简化了仿真设置步骤,缩短了从首次探索到发现更深层次问题的时间。

· PCIe AMI 建模器支持 NRZ 和 PAM4 调制,能够快速生成 PCIe 系统分析所需的 AMI 模型。AMI 模型生成器为设计师提供了一套向导式的 AMI 模型生成工作流程,可快速创建发射器(Tx)和接收器(Rx)模型。

· 采用经过简化的、由仿真驱动的虚拟合规性测试,使得设计人员能够确保设计的质量。高度集成的、由仿真驱动的 PCIe 合规性测试工作流程可最大限度地减少设计迭代,缩短产品上市时间,从而降低设计成本。

Chiplet PHY Designer的增强功能

· Chiplet PHY Designer 是 EDA 行业首款针对通用小芯片互联技术 (UCIe) 标准的仿真解决方案,有助于评估和预测芯片到芯片的链路裕量、用于通道合规性分析的 VTF 以及前向时钟的性能。Chiplet PHY Designer 具有全新的设计探索和报告生成能力,可加速信号完整性分析和合规性验证,从而提高设计人员的工作效率,缩短新产品的上市时间。

是德科技EDA 事业部高速数字产品线总监 Hee-Soo Lee 表示:“我们将持续拓展由标准驱动的工作流程解决方案,从而为客户提供支持。与同类产品相比,我们的高速数字产品组合能够为信号完整性分析和合规性测试验证提供更准确、更先进的仿真软件,在 EDA 行业处于领先地位。PCIe 和 UCIe 等数字标准对于保障电子系统的性能而言至关重要。设计师在工作过程中使用是德科技的 PCIe 和 UCIe 仿真解决方案,可以缩短开发周期,节省大量时间和成本。”

- 下一篇:是德科技加入汽车连接联盟以支持汽车创新

- 上一篇:一文读懂丨冰水冲击试验介绍

广告

广告 编辑推荐

最新资讯

-

《汽车隔声性能测量与评价方法 第2部分:消

2026-03-12 13:53

-

《汽车隔声性能测量与评价方法 第1部分:混

2026-03-12 13:53

-

动力性试验:从驱动力模型到道路试验

2026-03-12 13:53

-

联合国法规R87对机动车白天行车灯的工程化

2026-03-12 12:20

-

正式实施:国标推动“电动土方机械行业”深

2026-03-12 09:31

广告

广告