GaN HEMT可靠性:浪涌应力下级联GaN HEMT鲁棒性评估

用于汽车动力总成和电网等具有挑战性应用的功率器件必须具有浪涌能量鲁棒性。虽然Si和SiC MOSFET可以通过雪崩耗散浪涌能量,但GaNHEMT没有雪崩能力。本文探讨了额定电压为650V级联GaN HEMT在无钳位电感开关(UIS) 测试中的重复浪涌能量鲁棒性。浪涌能力和在此应力下的安全工作区是GaN HEMT整体可靠性的关键方面。

氮化镓HEMT可靠性:浪涌能量鲁棒性

与Si和SiC MOSFET不同,GaN HEMT不具有固有的雪崩能力,因为源极和漏极之间缺乏p-n结[1]。根据最近的研究,器件输出电容和负载电感器之间的谐振能量传输使得增强模式(E模式)p栅GaN HEMT能承受浪涌能量。GaN HEMT的漏源电压(VDS)在此传输过程中表现出谐振波形。当峰值谐振电压达到器件的动态击穿电压(BV)时,该电压可能与其静态BV [2]、[3]明显不同,器件在瞬态时失效。

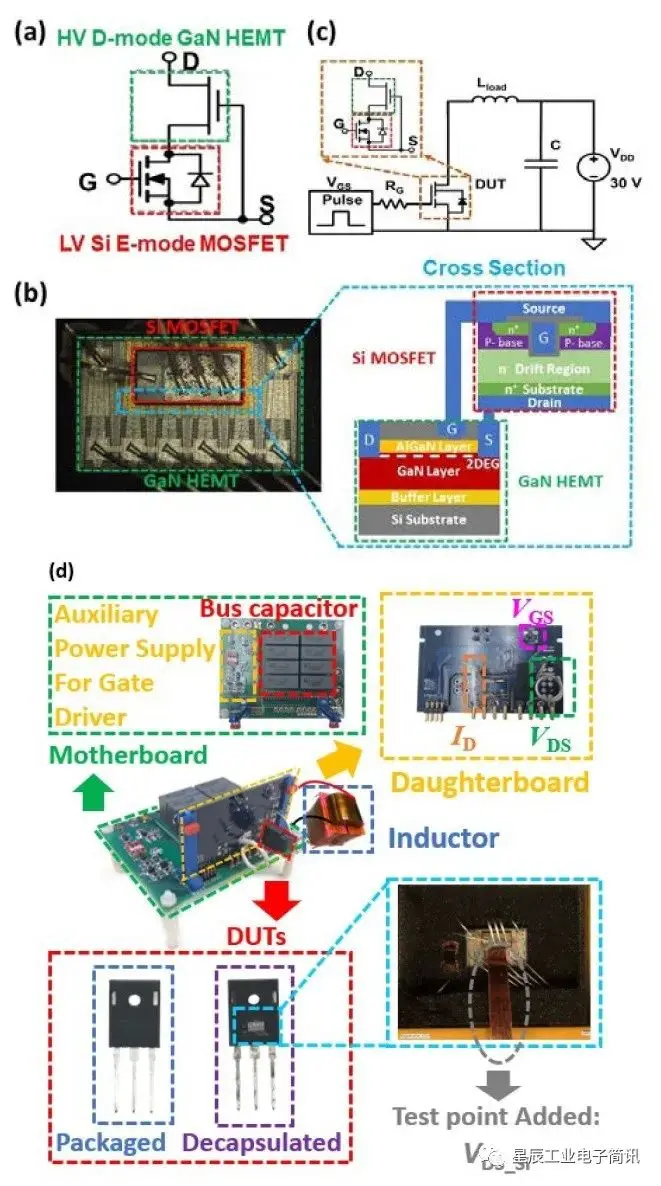

级联氮化镓HEMT用作单个E型高压器件,由E型低压硅MOSFET和耗尽模式(D型)高压氮化镓HEMT组成(图1a)。研究发现,级联GaN HEMT可靠性在重复浪涌能量应力下的失效边界小于单一应力下的失效边界。由于重复的浪涌能量应力,该器件还表现出显著的退化。

图1:(a)级联 GaN HEMT的等效电路图。(b)去除封装的HEMT照片。(c)UIS测试设置电路图。(d)级联GaN HEMT包含封装及去除封装的UIS测试系统照片。

单事件UIS测试

被测器件(DUT)是一款商用650V、50mΩ级联氮化镓 HEMT(图 1b),采用TO-247封装[4]。堆叠在GaN HEMT上的是一个垂直结构的SiMOSFET,其漏极焊盘与GaN HEMT的源极焊盘电连接。SiMOSFET的雪崩击穿电压(BVAVA)为35V,HEMT的阈值电压(Vth)为-22 V。

UIS测试电路的原理图如图1c所示。UIS测试包括两个步骤。第一步,DUT导通,负载电感由VDD充电;第二步,DUT被关断,存储在电感中的能量被迫通过DUT流通。图1d显示了UIS评估系统的图像,其中包括主板(带有主电源环路和母线电容器)和一个子板(带有DUT和三个测试点)。

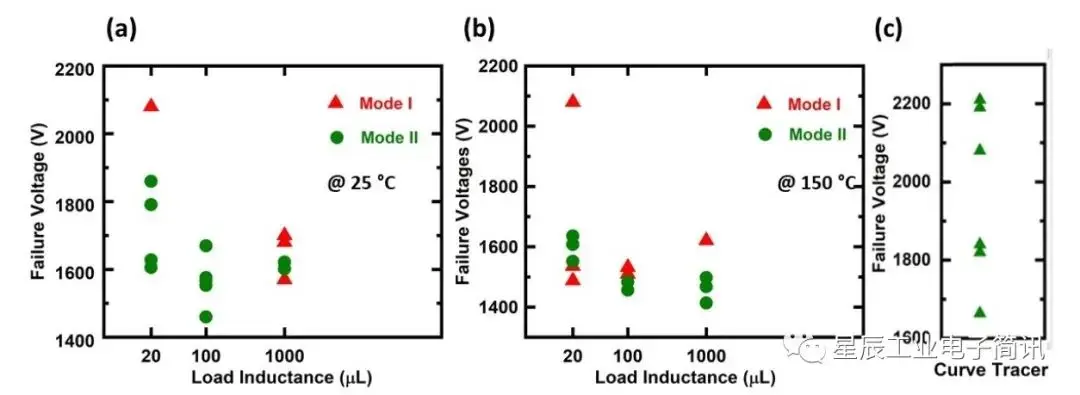

在研究单事件UIS应力下的GaN HEMT可靠性时,观察到级联GaNHEMT的两种失效模式:HEMT漏极和栅极之间的短路以及HEMT漏极和源极之间的短路。图2(a)和(b)分别总结了在30°C和25°C三种不同大小的负载电感下测得的150个DUT的故障模式和故障电压。图2(c)显示了曲线示图仪上6个DUT的BV测量结果。这些结果表明,在单事件UIS应力下,第二失效模式更加一致。

图2:在(a)25°C 和(b)150°C下测试的多个级联GaN HEMT的故障电压。(c)曲线示图器DC测量中测量的多个级联GaN HEMT的静态 BV。

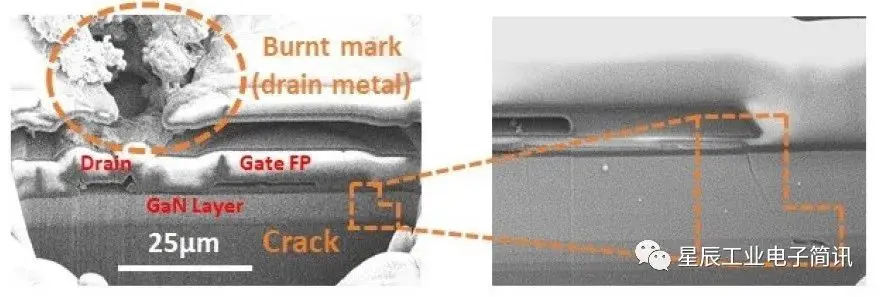

在此模式下失效的DUT横截面扫描电子显微镜(SEM)图像如图3所示。

图3:GaN HEMT失效点区域的横截面SEM图像,揭示了漏极金属的损坏以及从栅极延伸到GaN缓冲层和过渡层的裂纹。

重复的UIS测试

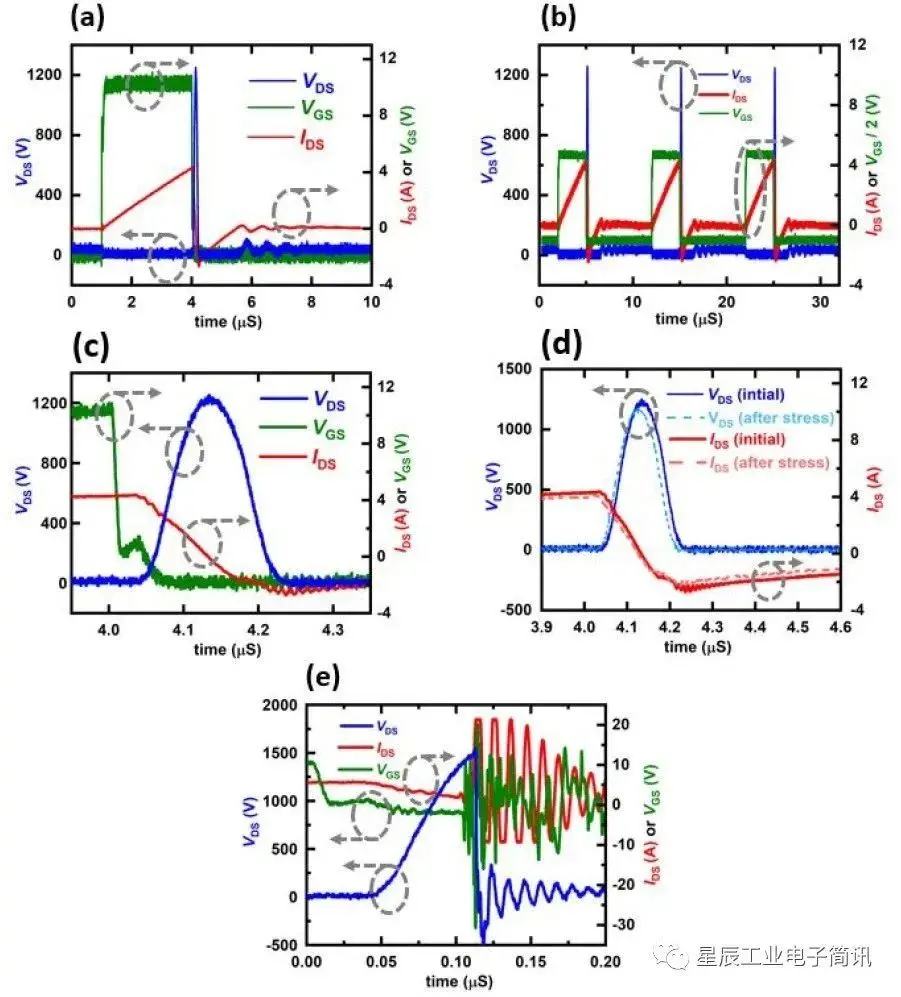

对于这些重复的UIS测试,脉冲周期固定为10 μs。每个UIS脉冲期间的电感充电周期通常约为3 μs,并且在整个特定的重复UIS测试中固定,调制峰值VDS。峰值电压为1.25 kV的单个UIS应力下的DUT波形如图4a所示,在相同峰值电压的重复UIS应力下的波形如图4b所示,单事件UIS测试期间DUT的放大波形如图4c所示。最后,图4d显示了100万周期重复UIS应力的初始和最后阶段DUT的波形比较,而图4e显示了UIS测试下DUT的故障波形,验证了峰值瞬态VDS故障,即与p栅极GaN HEMT相比,UIS故障行为相同[1]。

图4:(a)单个UIS应力和(b)重复UIS应力下的DUT 波形;(c)DUT在单个 UIS应力测试中的安全耐受波形放大图;(d)比较重复测试期间开始和结束阶段的UIS波形;(e)在UIS测试下DUT的故障波形,验证瞬态VDS处的故障;

总共测试了20个DUT多达100万个循环,以探索级联GaN HEMTS在重复UIS应力下的失效和退化。以了解重复UIS测试下的GaN HEMT可靠性并定义安全工作区。

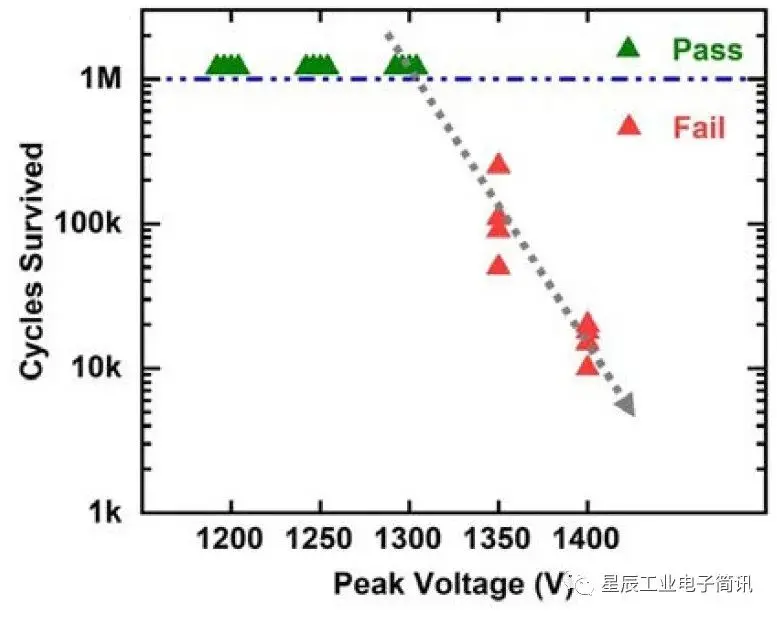

当峰值VDS超过1.35kV时,没有DUT通过1万次循环(图5)。发现DUT在1.4kV峰值VDS下可存活约10,000个周期,在1.35kV峰值VDS下可存活约100,000个周期。级联GaN HEMT在重复UIS应力(约1.3kV)下的真实失效边界低于单事件UIS应力和静态BV下的真实失效边界。

图5:对于20个DUT 的故障测试或最多1 M个周期的测试,可得到DUT在UIS应力测试中能承受的周期是峰值VDS的函数。

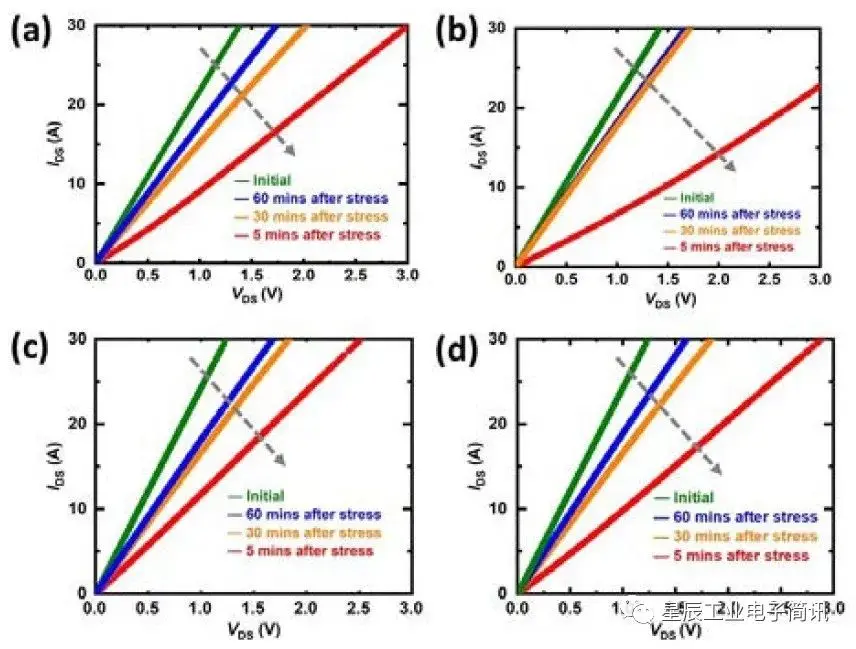

在25°C和150°C下,在100万周期UIS应力下测试了总共4个DUT,峰值电压分别为1.25kV和1.3kV,以检查DUT退化与UIS峰值电压和温度之间的相关性。所有4个DUT 都表现出非常相似的退化和恢复行为(图6)。在相同条件下测试了其它DUT产品,证实DUT退化/恢复行为与峰值UIS VDS或温度之间几乎没有统计学上的显着相关性。

图6:在100万次UIS应力循环前后DUT的IDS-VDS演变(VGS = 1V),其中(a) 25°C时,峰值电压1.25kV;(b)150°C时,峰值电压1.25kV;(c)25°C时,峰值电压为1.3kV,(d)150°C时,1.3kV过压应力;

GaN HEMT浪涌可靠性解释

GaN HEMT中的缓冲捕获积累可以解释重复UIS应力下DUT的退化和恢复特性。高VDS使得电子更容易在每个UIS应力期间注入GaN缓冲区,无论它们来自源还是过渡层与p型硅衬底之间的界面。缓冲陷阱预计会累积,甚至在重复的 UIS应力下可能饱和。

二维电子气体(2DEG)会被缓冲层捕获的电子耗尽,从而升高RDS(ON)。在此期间,被俘虏的电子将提高耗尽区域的屏障,从而导致较低的IDSS。最后,缓冲层捕获将扩大耗尽区域,从而解释为什么CDS在UIS应力之后下降。缓冲层中被捕获的电子随着恢复期的延长而逐渐被释放,这是观察到的参数飘移恢复缓慢的原因。

与单事件UIS测试中的故障边界(峰值VDS)相比,重复UIS测试中的故障边界(峰值VDS)较低,这可以解释为由于缓冲区捕获更明显而导致的较低动态BV。

TCAD器件仿真已在Silvaco Atlas中进行,模拟器件结构由去封装的DUT的显微图像确定。该模型证实,当峰值电压低于1.3kV时,DUT能够承受100万次UIS循环,但表现出显著的参数飘移,包括RDS(ON)增加,IDSS降低和CDS降低。这些参数偏移大部分可以在一小时后恢复。上述器件故障和退化行为可以通过GaN HEMTS中缓冲层捕获的积累以及动态BV的相关变化来解释。这些结果加深了对级联GaN HEMT鲁棒性的理解,并为其转换器设计裕量提供了关键参考。

参考文献:

[1] R. Zhang, J.P. Kozak, M. Xiao, J. Liu, and Y. Zhang, “Surge-Energy and OvervoltageRuggedness of P-Gate GaN HEMTs,” IEEE Trans. Power Electron., vol. 35, no. 12,pp. 13409–13419, Dec. 2020.

[2] R. Zhang, J.Kozak, Q. Song, M. Xiao, J. Liu, and Y. Zhang, “Dynamic Breakdown Voltage ofGaN Power HEMTs”, 2020 66th IEEE International Electron Devices Meeting (IEDM),pp. 23.3.1-23.3.4, Dec. 2020.

[3] J. P. Kozak,R. Zhang, Q. Song, J. Liu, W. Saito, and Y. Zhang, “True Breakdown Voltage andOvervoltage Margin of GaN Power HEMTs in Hard Switching,” IEEE Electron DeviceLetters, early access online, Mar. 2021. doi: 10.1109/LED.2021.3063360.

[4] “TP65H050WS650V Cascode GaN FET,” Transphorm.https://www.transphormusa.com/en/product/tp65h050ws-2/ (accessed Jan. 16,2021).

广告

广告 最新资讯

-

联合国法规R76对轻便摩托车前照灯远近光性

2026-03-10 12:15

-

联合国法规R75对摩托车与轻便摩托车气压轮

2026-03-10 12:14

-

联合国法规R74对L1类车辆灯光与光信号装置

2026-03-10 12:14

-

联合国法规R73对货车侧面防护装置的工程化

2026-03-09 12:14

-

联合国法规R72对HS1卤素灯摩托车前照灯的工

2026-03-09 12:13

广告

广告